PACT 2007 Program

The PACT 2007 tutorials and workshops will be held

Saturday September 15 and Sunday September 16 - see the

Tutorials and Workshops Schedule

for details.

The PACT 2007 technical sessions will be held

Monday September 17 through Wednesday September 19

at the conference hotel,

the

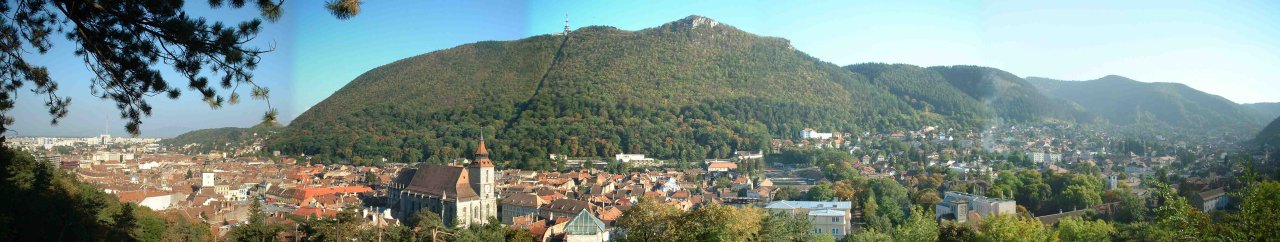

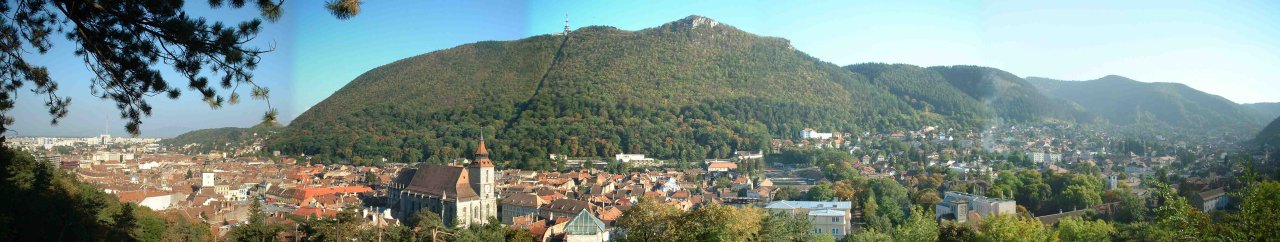

ARO Palace Hotel.

|

PACT 2007 Program - Sunday, September 16, 2007

|

| 18:00 |

Organ Concert in the Black Church & Dinner at Cerbul Carpatin

|

|

PACT 2007 Program - Monday, September 17, 2007

|

| 8:45-9:00 |

Opening Remarks

Ion Vişa, President of Transilvania University of Brasov

Marc Snir, PACT General Chair

|

| 9:00-10:00 |

Keynote:

Bjarne Stroustrup,

Write clean (parallel) code!

Session Chair: Lawrence Rauchwerger

|

| 10:00-10:30 |

Break

|

| 10:30-12:00 |

Hardware Track (Session 1): Systems

Session Chair: Thomas Gross

Architectural Support for the Stream Execution Model on General-Purpose Processors

Jayanth Gummaraju, Mattan Erez, Joel Coburn, Mendel Rosenblum and William Dally

A Flexible Heterogeneous Multi-Core Architecture

Miquel Pericas, Ruben Gonzalez, Adrian Cristal, Francisco Cazorla, Daniel A. Jimenez

and Mateo Valero

Improving Performance Isolation on Chip Multiprocessors via an Operating System Scheduler

Alexandra Fedorova, Margo Seltzer and Michael Smith

|

| |

Software Track (Session 2): Pipelining

Session Chair: Kemal Ebcioglu

Software-Pipelining on Multi-Core Architectures

Alban Douillet and Guang R. Gao

Speculative Decoupled Software Pipelining

Neil Vachharajani, Ram Rangan, Easwaran Raman, Matthew Bridges, Guilherme Ottoni and David August

Rotating Register Allocation for Enhanced Pipeline Scheduling

Suhyun Kim and Soo-Mook Moon

|

| 12:00-14:00 |

Lunch

|

| 14:00-16:00 |

Hardware Track (Session 3): Verification & Security

Session Chair: Michael Gschwind

Unified Architectural Support for Soft-Error Protection or Software Bug Detection

Martin Dimitrov and Huiyang Zhou

Verification-Aware Microprocessor Design

Anita Lungu and Daniel Sorin

I2SEMS: Interconnects-Independent Security Enhanced Shared Memory Multiprocessor Systems

Manhee Lee, Minseon Ahn and Eun Jung Kim

Error Detection Using Dynamic Dataflow Verification

Albert Meixner and Daniel Sorin

|

| |

Software Track (Session 4): Optimizations

Session Chair: Ayal Zaks

Extending Object-Oriented Optimizations for Concurrent Programs

Kelly Heffner, Michael D. Smith and David Tarditi

Language and Virtual Machine Support for Efficient Fine-Grained Futures in Java

Lingli Zhang, Chandra Krintz and Priya Nagpurkar

Call-chain Software Instruction Prefetching in J2EE Server Applications

Priya Nagpurkar, Harold Cain, Mauricio Serrano, Jong-Deok Choi and Chandra Krintz

Detecting Change in Program Behavior for Adaptive Optimization

Nitzan Peleg and Bilha Mendelson

|

| 16:00-18:00 |

Poster Session

Poster Listing

|

| 18:00 |

Conference Banquet

Sponsored by Google

|

|

PACT 2007 Program - Tuesday, September 18, 2007

|

| 9:00-10:00 |

Keynote:

Fran Allen,

Compilers and Multi-Cores: A Performance Partnership or Missed Opportunity?

Session Chair: Marc Snir

|

| 10:00-10:30 |

Break

|

| 10:30-11:30 |

Hardware Track (Session 5): Saving Energy

Session Chair: Gabriel Silberman

Reducing Energy Consumption of On-Chip Networks Through a Hybrid Compiler-Runtime Approach

Guangyu Chen, Feihui Li and Mahmut Kandemir

An Energy Efficient Parallel Architecture Using Near Threshold Operation

Ronald Dreslinski, Bo Zhai, Trevor Mudge, David Blaauw and Dennis Sylvester

|

| |

Software Track (Session 6): Algorithms

Session Chair: Albert Cohen

AA-Sort: A New Parallel Sorting Algorithm for Multi-Core SIMD Processors

Hiroshi Inoue, Takao Moriyama, Hideaki Komatsu and Toshio Nakatani

The Fault Tolerant Parallel Algorithm: the Parallel Recomputing Based Failure Recovery

Xuejun Yang, Yunfei Du, Panfeng Wang, Hongyi Fu, Jia Jia, Zhiyuan Wang and Guang Suo

|

| 12:00 |

Conference Excursion

|

|

PACT 2007 Program - Wednesday, September 19, 2007

|

| 9:00-10:00 |

Keynote:

Yale Patt,

Harnessing the Transformation Hierarchy

Session Chair: Lawrence Rauchwerger

|

| 10:00-10:30 |

Break

|

| 10:30-12:30 |

Hardware Track (Session 7): Processors

Session Chair: Nacho Navarro

Paceline: Improving Single-Thread Performance in Nanoscale CMPs

through Core Overclocking

Brian Greskamp and Josep Torrellas

Early Register Release for Out-of-Order Processors with Register Windows

Eduardo Quiñones, Joan-Manuel Parcerisa and Antonio González

L1 Cache Filtering Through Random Selection of Memory References

Yoav Etsion and and Dror G. Feitelson

Effective Management of DRAM Bandwidth in Multicore Processors

Nauman Rafique, Won-Taek Lim and Mithuna Thottethodi

|

| |

Software Track (Session 8): Compilers

Session Chair: Jaejin Lee

A Loop Correlation Technique to Improve Performance Auditing

Jeremy Lau, Matthew Arnold, Brad Calder and Michael Hind

Latency Hiding in Multi-Threading and Multi-Processing of Network Applications

Xiaofeng Guo, Jinquan Dai, Long Li, Zhiyuan Lv and Prashant R. Chandra

Introducing Control Flow into Vectorized Code

Jaewook Shin

Automatic Correction of Loop Transformations

Nicolas Vasilache, Albert Cohen and Louis-Noel Pouchet

|

| 12:30-14:30 |

Lunch

|

| 14:00-14:30 |

Funding Opportunities - NSF/CISE Directorate

(full version (pdf),

short version (pdf))

Almadena Chtchelkanova, Program Director, NSF

|

| 14:30-16:30 |

Hardware Track (Session 9): Modeling & Measurement

Session Chair: James Cownie

FAME: FAirly MEasuring Multithreaded Architectures

Javier Vera, Francisco J. Cazorla, Alex Pajuelo, Oliveiro J. Santana, Enrique Fernandez and Mateo Valero

CIGAR: Application Partitioning for a CPU/Coprocessor Architecture

John Kelm, Isaac Gelado, Mark Murphy, Nacho Navarro, Steve Lumetta and Wen-mei Hwu

Using Predictive Modeling for Cross-Program Design Space Exploration in Multicore Systems

Salman Khan, Polychronis Xekalakis, John Cavazos and Marcelo Cintra

CacheScouts: Fine-Grain Monitoring of Shared Caches in CMP Platforms

Li Zhao, Ravi Iyer, Ramesh Illikkal, Jaideep Moses, Don Newell and Srihari Makineni

|

| |

Software Track (Session 10): Transactional Memory & Locks

Session Chair: Andreas Moshovos

Component-Based Lock Allocation

Richard L. Halpert, Christopher J. F. Pickett and Clark Verbrugge

JudoSTM: A Dynamic Binary Rewriting Approach to Software Transactional Memory

Marek Olszewski, Jeremy Cutler and J. Gregory Steffan

The OpenTM Transactional Application Programming Interface

Woongki Baek, Chi Cao Minh, Martin Trautmann, Christos Kozyrakis and Kunle Olukotun

A Study of a Transactional Parallel Routing Algorithm

Ian Watson, Chris Kirkham and Mikel Lujan

|

| 16:30 |

Conference Closing

|

|